The following announcement of a fellow Cornell alum Mark Charney on his linkedin page

https://www.linkedin.com/feed/update/urn:li:activity:6815764405725270016/ caught my eye today

where Mark is celebrating the receipt of his 100th US patent.I especially liked the comment about collaboration. That has always been the most interesting aspect of the inventive and technical development process.

To that end, I roamed over to https://en.wikipedia.org/wiki/List_of_prolific_inventors to see about other Intel inventors, and to my surprise, I saw 30 Intel inventors listed. I believe that I have mentioned this site before in earlier postings, too, http://vzimmer.blogspot.com/2014/08/ http://vzimmer.blogspot.com/2021/01/innovation-and-invention-redux.html.

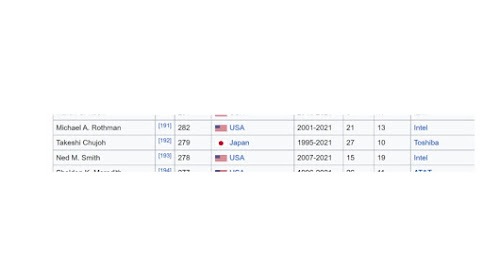

Two immediate collaborators I recognize are Ned Smith and Mike Rothman.

I am a co-inventor on 272 of Mike's (96%) issued US patents and 27 of Ned's (9.7%)Ned has a pretty interesting publication history, too, with dblp picking up https://dblp.org/pid/56/3580.html. This compares to my dblp list https://dblp.org/pid/34/5641.html. Regrettably no joint publications, although I'm a big fan of Ned's Clark Wilson integrity model study of the TPM. We cited this in https://link.springer.com/book/10.1007/978-1-4842-6106-4, for example, along with his IOT security book. That paper was presented at the Security and Management (SAM) conference in Las Vegas. I published my first four papers in the 2000's at that venue, too. If I recall Selim Aissi https://www.linkedin.com/in/aissi/ encouraged folks to contribute to that venue?

I spent time working with Ned when he was the VPro security architect, too https://www.intel.com/content/dam/www/public/us/en/documents/research/2008-vol12-iss-4-intel-technology-journal.pdf. And it looks like Ned and I were co-inventors on my latest issued patent "Static and dynamic device profile reputation using cloud-based machine learning" 11,049,039 along with our erstwhile McAfee colleagues.

As for Mike Rothman, he has been a long-time collaborator (and physical office neighbor when we aren't in COVID seclusion). Mike overlaps on my dblp above with a couple of books and we also contribute to the firmware standards, including the review of the UEFI ecosystem in https://www.intel.com/content/dam/www/public/us/en/documents/research/2011-vol15-iss-1-intel-technology-journal.pdf.

Perusing the list further I see David Durham with whom I collaborated on a few patents

or 4% of his total 216. And finally, one joint patent with another Cornell alum Gil Neiger

out of his 211 patents (0.5%) as of July 6, 2021, along with some of the other Intel virtualization crowd https://ieeexplore.ieee.org/document/1430631.

Although Neiger and Charney are Cornell alums, they are Phd's & I am but a BSEE from Cornell and MS Comp Sci from UW here in Seattle. I was reminded of my lowly spot on the tech education totem pole when shopping at Fred Meyer in Issaquah, WA last night and two customers were loudly speaking with each other in the vegetable section. I caught the fragment of their conversation "...and he only has an MS and not even a Phd." I didn't recognize the two but at that point I seriously doubted my credentials to buy that bundle of organic carrots I had in my hand....

Although we are not co-inventors on any patents, my more immediate neighbors on the https://en.wikipedia.org/wiki/List_of_prolific_inventors list include the number one Intel inventor Robert Chau https://newsroom.intel.com/news/creating-new-technologies-keep-moores-law-alive-well/ and number three inventor Jack Kavalieros https://www.intel.com/content/www/us/en/newsroom/news/2021-inventor-year.html#gs.55miv2

who bound me from above with Chau's 486 patents, my 453, and Jack's 440 below, respectively.The other good thing about Jack passing my count will be maintaining grade monotonicity. Instead of Fellow->Sr. PE->Sr. Fellow as we have today with Jack->Vincent->Robert, we'll have Sr. PE->Fellow->Sr. Fellow, where grade level will increase on the Y-axis as patent count increases on the X-axis.