This is the inaugural blog entry of 2025. I used to try to have at least one posting per month, but the last couple of years have demonstrated something of a slowdown.

In lieu of my Anniversary.Next^ postings like https://vzimmer.blogspot.com/2024/02/27-or-anniversarynext12-ai-runtime.html which tracked the latter portion of my Intel journey, I have to find another temporal indicator to inspire a posting.

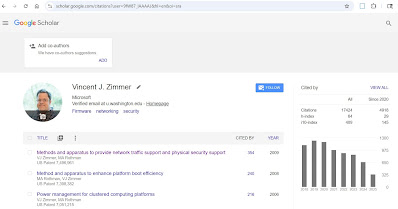

To that end, Monday 2/24/25 made 33 years of working full-time post undergrad (2/24/1992). Someone who I admired a lot and retired on the same day from MS contacted me recently to check-in. I told him that I re-entered the workforce and he replied with "RETIREMENT FAIL!" I opined that maybe it's a case of a prisoner that misses his prison cell? Speaking of cells, I now have a named one:

Another quote I recall was that if you are still working in tech in your 50's then you are 'doing it wrong.' Oops. From Intel "Rule of 75" for retirement to the IRS "Rule of 55" for 401k's, quite a flurry of "Rules of..." these last 6 months.

To move from corporate and government 'rules' into levity, an icebreaker event that occurred a couple of months back was a bit amusing. It entailed a large business conference call where participants were asked to share their favorite reality TV show in the Teams poll. The host berated the crowd for the many mentions of Severance https://en.wikipedia.org/wiki/Severance_(TV_series) in the result stream as demonstrating a misunderstanding of the question. I personally don't believe the respondents were so confused after all. "Perks" anyone https://www.teamblind.com/post/Microsoft-Perks-7yf2EYnJ https://severance.wiki/perks?

BTW I've only seem fragments of Severance when passing by my younger daughter watching it so I may have have drawn some false equivalences from my scant data. I'm just saying.....

Speaking of questions, the in-person q/a with sci-fi author https://en.wikipedia.org/wiki/Cory_Doctorow were quite interesting at a local book store.

I soldiered through the long line to get an autograph at the end of the evening

and mentioned that I worked on UEFI. I wanted to stimulate a conversation given some of the points he made online in venues like https://doctorow.medium.com/your-computer-is-tormented-by-a-wicked-god-e90205ed80d7 and https://pluralistic.net/2024/01/18/descartes-delenda-est/, viz.,

After I told Corey what I worked on, he asked where. After the latter response I could see that he tensed tensed up. I eased situation by saying his voice was important, especially with the passing of folks like Ross Anderson https://vzimmer.blogspot.com/2024/03/a-legend-passes.html and his positions on the topic https://www.lightbluetouchpaper.org/2011/09/20/trusted-computing-2-0/.

Doctorow had a lot of good quotes in his talk, such as "you cannot reason someone out of a position into which they haven't first reasoned themselves into." I should dig into my notes and share out a few other of the fragments from that evening.

From 3rd Place books back to one of my favorite locations at Microsoft, the Microsoft library

And visiting with some former Intel colleagues now working at AMD and non-Redmond MS site, respectively.

Again, sometimes on these cross-campus treks I stop at the Microsoft Library in building 92. It's interesting to see which of the firmware books have been checked out at various times, viz.,

Sticking to the topics of books, at my local building, co-worker Jose visited again after having

our Thanksgiving time https://vzimmer.blogspot.com/2024/11/turbulent-weather-books-and-new-jobs.html posting to get his trio of firmware-related Apress https://link.springer.com/book/10.1007/978-1-4842-6106-4 https://link.springer.com/book/10.1007/978-1-4842-7974-8 https://link.springer.com/book/10.1007/978-1-4842-7939-7 books signed.

The security book I'm holding has a section on Rust https://link.springer.com/book/10.1007/978-1-4842-6106-4

as does

https://link.springer.com/book/10.1007/978-1-4842-7974-8

As such, it was nice to see Rust and firmware mentioned in https://www.youtube.com/watch?v=1VgptLwP588

Good stuff.

On a sad parting note on the topic of technical books, Stuart Douglas

passed away recently.

After a career at Intel working on things like RMX, he pivoted into technical publishing. He was my contact at Intel Press for a series of publications, including the 2006 first edition of Beyond BIOS

https://www.amazon.com/Beyond-BIOS-Implementing-Extensible-Interface/dp/0974364908

It looks like Stuart's Linkedin page is still active, though

And speaking of LI, I sometimes find 'interesting' bread crumbs of visitors to my site.

A recent list of visitors looks mostly usual other than the USG viewer at the bottom

And then there was 30

for my sporadic IEEE membership since my Cornell undergrad days.

Nice round #'s to close this inaugural 2025 blog entry.

fin